計(jì)算機(jī)為何采用二進(jìn)制 計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)開發(fā)的基石

計(jì)算機(jī)系統(tǒng)采用二進(jìn)制作為其信息表示和處理的基礎(chǔ),這一設(shè)計(jì)選擇并非偶然,而是源于其技術(shù)實(shí)現(xiàn)的便捷性、可靠性與邏輯一致性,并為后續(xù)計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)的發(fā)展奠定了至關(guān)重要的理論基礎(chǔ)與物理基礎(chǔ)。

從物理實(shí)現(xiàn)層面看,二進(jìn)制與電子元件的特性高度契合。計(jì)算機(jī)的基本電路由數(shù)以億計(jì)的晶體管構(gòu)成,這些晶體管本質(zhì)上是一種電子開關(guān),其狀態(tài)易于在“開”(通常代表高電壓,邏輯值1)與“關(guān)”(通常代表低電壓,邏輯值0)之間穩(wěn)定、快速且可靠地切換。這種二態(tài)性直接對(duì)應(yīng)了二進(jìn)制的“0”和“1”。相比于模擬信號(hào)或更高進(jìn)制的表示(如十進(jìn)制),二進(jìn)制信號(hào)的抗干擾能力強(qiáng),容錯(cuò)率高,因?yàn)樵陔娐吩肼曄拢瑓^(qū)分“高”與“低”兩種狀態(tài)遠(yuǎn)比區(qū)分多個(gè)不同的電壓等級(jí)要簡(jiǎn)單和穩(wěn)定。這使得基于二進(jìn)制的數(shù)字電路設(shè)計(jì)簡(jiǎn)潔、高效且成本可控。

從邏輯運(yùn)算與數(shù)學(xué)層面看,二進(jìn)制與布爾代數(shù)完美對(duì)應(yīng)。19世紀(jì)喬治·布爾建立的布爾代數(shù),其變量取值僅為“真”與“假”,這恰好可以用二進(jìn)制的“1”和“0”來表示。計(jì)算機(jī)中央處理器(CPU)的核心——算術(shù)邏輯單元(ALU)——所執(zhí)行的所有復(fù)雜運(yùn)算(加、減、乘、除、邏輯比較等),最終都可以分解為一系列基于“與”、“或”、“非”等基本邏輯門的二進(jìn)制操作。這種數(shù)學(xué)上的簡(jiǎn)潔性和一致性,使得用硬件電路實(shí)現(xiàn)復(fù)雜的計(jì)算和控制邏輯成為可能,并確保了計(jì)算過程的絕對(duì)精確(在數(shù)字域內(nèi))。

二進(jìn)制極大地簡(jiǎn)化了數(shù)據(jù)在計(jì)算機(jī)內(nèi)部的存儲(chǔ)、傳輸和處理。無論是數(shù)字、文本、圖像、聲音還是視頻,所有類型的數(shù)據(jù)在計(jì)算機(jī)中最終都被編碼為二進(jìn)制位(bit)序列。存儲(chǔ)設(shè)備(如內(nèi)存、硬盤)通過磁化方向、電荷有無等物理方式記錄“0”和“1”;處理過程則是按位對(duì)這些序列進(jìn)行操作。這種統(tǒng)一的表示方法,為計(jì)算機(jī)體系結(jié)構(gòu)的設(shè)計(jì)提供了極大的靈活性。

二進(jìn)制對(duì)計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)開發(fā)的深遠(yuǎn)影響

計(jì)算機(jī)采用二進(jìn)制這一根本特性,直接塑造了計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)的開發(fā)路徑與核心協(xié)議:

- 數(shù)據(jù)傳輸?shù)幕?/strong>:計(jì)算機(jī)網(wǎng)絡(luò)傳輸?shù)摹皵?shù)據(jù)包”,其本質(zhì)就是二進(jìn)制比特流。網(wǎng)絡(luò)協(xié)議棧(如TCP/IP)的每一層,其協(xié)議頭和數(shù)據(jù)載荷都以二進(jìn)制格式定義。物理層負(fù)責(zé)將二進(jìn)制比特轉(zhuǎn)換為光、電或無線電波信號(hào)進(jìn)行傳輸(如用不同的電壓、光脈沖頻率代表0和1),并在接收端準(zhǔn)確還原。沒有二進(jìn)制這種簡(jiǎn)單、規(guī)范的表示法,就無法實(shí)現(xiàn)高效、標(biāo)準(zhǔn)化的數(shù)據(jù)編碼與解碼。

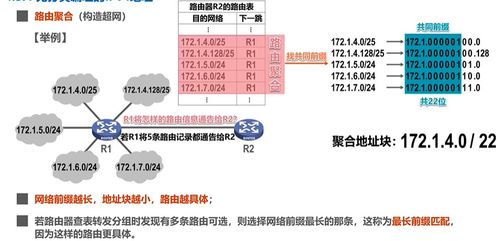

- 尋址與路由的基礎(chǔ):計(jì)算機(jī)網(wǎng)絡(luò)中的關(guān)鍵標(biāo)識(shí),如IP地址(IPv4的32位、IPv6的128位)和MAC地址(48位),都是用二進(jìn)制數(shù)字表示。路由器進(jìn)行路由決策、交換機(jī)進(jìn)行數(shù)據(jù)幀轉(zhuǎn)發(fā),其核心算法正是基于對(duì)這些二進(jìn)制地址的匹配和查找。二進(jìn)制的位操作(如與、或、移位)是高效實(shí)現(xiàn)子網(wǎng)劃分、路由聚合等網(wǎng)絡(luò)管理功能的基礎(chǔ)。

- 協(xié)議設(shè)計(jì)與檢錯(cuò)糾錯(cuò):網(wǎng)絡(luò)協(xié)議中大量的控制字段、狀態(tài)標(biāo)志位,天然地使用二進(jìn)制位來表示(例如TCP報(bào)文頭中的SYN、ACK、FIN等標(biāo)志位)。為了保證數(shù)據(jù)傳輸?shù)目煽啃裕W(wǎng)絡(luò)技術(shù)廣泛采用了基于二進(jìn)制運(yùn)算的檢錯(cuò)碼(如奇偶校驗(yàn)、CRC循環(huán)冗余校驗(yàn))和糾錯(cuò)碼。這些算法高效地利用了二進(jìn)制位的特性來檢測(cè)和修正傳輸過程中因干擾產(chǎn)生的比特錯(cuò)誤。

- 促進(jìn)了標(biāo)準(zhǔn)化與互操作性:二進(jìn)制作為一種全球通用的“機(jī)器語言”,使得不同廠商、不同架構(gòu)的計(jì)算機(jī)和網(wǎng)絡(luò)設(shè)備能夠相互通信。只要遵循共同的二進(jìn)制協(xié)議規(guī)范,設(shè)備就能理解彼此發(fā)送的數(shù)據(jù)包含義。這是互聯(lián)網(wǎng)能夠全球互聯(lián)互通的前提。

計(jì)算機(jī)采用二進(jìn)制,是由其物理實(shí)現(xiàn)的可行性、數(shù)學(xué)邏輯的簡(jiǎn)潔性以及工程上的可靠性共同決定的。這一根本選擇,不僅構(gòu)成了計(jì)算機(jī)硬件的核心設(shè)計(jì)原則,也成為了計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)得以誕生和發(fā)展的“通用語”與“原子單元”。從芯片內(nèi)部的微操作到橫跨全球的數(shù)據(jù)傳輸,二進(jìn)制為整個(gè)數(shù)字世界提供了統(tǒng)一、堅(jiān)實(shí)且高效的基石。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.fpfgj.cn/product/66.html

更新時(shí)間:2026-01-09 12:00:16